DVB-T解调器的数据传输设计

作者:成都电子科技大学 陈伟 摘要:介绍了DVB-T解调器的整体结构,并设计了一种多模块间进行数据传输的机制,同时还设计了前FFT同步系统,其中包括了基带变换、粗符号同步和分数频率同步。 关键词:DVB-T同步多路交叉开关 在无线信道中存在着多径衰落,严重影响了数据传输速率的提高。而正交频分复用(OFDM)技术具有很好的抗多径能力,因此欧洲的DVB-T标准采用了OFDM技术进行高质量的视频传输。这项标准已经被世界上很多国家采纳为自己的地面数字电视传输标准。

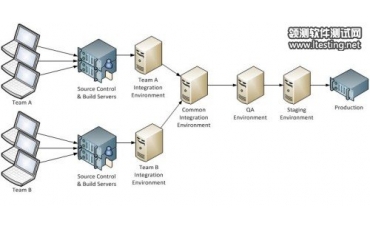

1 系统整体结构

系统设计的输入中频信号,直接对中频信号进行亚采样。系统分为前FFT同步、FFT、后FF向步与TPS解调、信道均衡与校正、信道解码五个模块。如图1所示。经过前FFT同步模块,数据被变换为速率为9.14MS/s的复数基带信号,同时去掉保护间隔;经FFT变换后数据被变换到领域;后FFT同步模块在频域中完成整数频偏的估计与校正、精符号偏移与采样率偏移的估计、TPS解调与导频提取;然后信道估计与均衡模块利用撮的导频进行CPE估计与校正、信道估计与均衡;接下来在信道解码模块中完成星座解映射、解符号交织、解化特交织、Viterbi译码、解卷积交织、RS译码、解能量扩散,最后输出TS流数据。

2 数据传输

解调器中包括5个大的模块,这5个模块之间的存在大量的数据交换。为了提高数据传输的效率并降低存储单元的消耗,笔者采用了如图2所示的以一个多路交叉开关为核心的数据传输模块来完成这5个模块之间的数据交换。

OPU-I表示5个模块,称为运算单元,而RAM-I表示5个RAM块,5个模块单元以流水线的方式交替使用这5个RAM块,流水线节拍如图3所示。OPU-0主要完成基带变换,,FFT前同步;OPU-1主要完成FFT变换;OPU-2主要完成FFT后同步;OPU-3主要完成信道仪态坏蛋均衡;OPU-4主要完成信道解码。其中一路地址的交叉开关如图4所示。

可以看出1bit地址信号的交叉开关需要5个四输入与门和1个五输入或门,总线按照32bit数据(双向)和12bit地址计算,则需要380个四输入与门和76个五输入或门,而且没有一路信号只经过两经门延迟。因此从实现规模和信号延迟上看,这个多路交叉开关都是容易实现的。这个模块在AlteraStratisx1S25FPGA上验证,其存取速度可以达到100MHz以上。

2.1基带变换模块

本系统设计的中频输入频率为36.5714MHz,亚采样速率为:27.42855MHz,设ω0=9.14285MHz,低通滤波器的通带归一化截止频率为0.277488966788,阻带归一化截止频率为0.3891776888786。通带内平坦度要求小于0.002dB,阻带抑制要求大小60dB,这个低通滤波器用一个74阶的FIR低通滤波器实现。基带变换模块结构如图5,其中NCO为数控振荡器,与一个复数乘法器一起完成基带变换、IQ分离和分数频偏极校正的功能,结构如图6所示。

复数乘法器采用Cordic算法实现,相位累加器根据输入的振荡频率调整相位累加的步长,其输出为本地载波的相位。Cordic乘法器的一个乘数为采样数据,另一个乘数就是本地载波的相位,其两个输出分别为输入数据与cos和sin相乘的结果。乘法器的输出进入上面所描述的74阶FIR低通,然后直接进行3倍抽取从而获得速率为9.14MS/s的数据基带信号。

2.2粗符号同步

粗符号同步模块包括粗符号同步估计、FFT窗位置调整、分数频率偏移估计。

2.2.1粗符号同步估计

粗符号同步和分频频偏采用基于TGI的联合估计算法,它利用TGI相关进行同步估计。具体算法参见参考文献,实现结构如图7所示。其中N_FFT=2048;N_TGI是保护间隔的长度,可以为N_FFT的1/32、1/16、1/8、1/4四个值。

在相关结果取绝对值后有一个峰值搜索和锁定环路,峰值搜索是为了寻找到粗符号同步位置,但是由于这个算法直接估计出的粗符号同步位置会有10个样点左右的抖动,这个抖动会影响后FFT同步的估计,因此这里引入一个锁定环路来稳定这个抖动。峰值搜索对过门限抽信号峰值进行搜索。

2.2.2FFT窗位置调整

FFT窗位置调整模块结果图如图8所示。利用粗符号同步信号同步地将数据写入深度为N_FFT+N_TGI的FIFO,粗符号同步调整控制模块产生输出数据的选通信号,以去掉TGI,实际是利用一个向下计数器,计数初始值由精符号同步估计出的精符号同步误差决定,计数器的启动由粗符号同步信号控制,当计数器下溢时停止计数,并产生输出使能信号。N_SYM=N_FFT+N_TGI。

2.2.3分数频偏锁定环路

图9为分数频偏锁定环路,其中FD为频率检测器,按照图7描述的算法进行分类频率偏移的估计。LF为环路滤波器,其传输函数为:(1+K1z-1)/(1+K2z-1)·|(1+K1)/(1+K2)|,其中K1=0.02,K2=-0.7,其频率响应如图10所示。

ACC为累加器。NCO即图5中所描述的数据振荡器。