64位微处理器体系结构发展回顾和展望

2002年8月秦皇岛市

张报昌先生现任中国惠普公司企业策划部政府关系高级经理,在此之前曾任康柏(中国)投资公司政府关系高级经理、高级技术顾问及Alpha芯片项目办公室主任。他曾在DEC电脑中国公司担任过主管对外关系的副总经理、市场部经理、高级技术顾问等职务。作为计算机方面的专家,张报昌先生是中国计算机学会体系结构专委会、信息存储专委会成员。他曾在1992年主持了Alpha芯片在中国的第一次发布和技术介绍,1994年组织出版了第一本公开发行的中文版Alpha芯片技术的书籍;并且在很多学术会议上发表过有关Alpha的技术报告和文章。他在参加DEC公司之前,曾在中国科学院高能物理研究所长期从事计算机的研究工作,在北京正负电子对撞机(BEPC)国家工程中担任高级职务,负责该工程的计算中心的建设。

内容提要:本文从回顾和分析64位微处理器历史、现状,未来发展出发,说明Intel和HP合作开发的IA-64 EPIC体系结构IPF系列的先进性和开放性以及发展潜力,它将要取代64位RISC芯片成为未来系统设计和企业应用的主流平台。本文对Alpha芯片的发展史作了回顾和评述,还分析对比各主要厂商应对这一发展潮流的64位微处理器战略和发展前景。

目录

引言1一、历史的回顾11.1. RISC体系结构的发展11.2. Alpha开创64位RISC计算新时代21.3. Intel推出第一代IPF系列产品Itanium 13

1.3.1. IA-64的基本设计思想3

1.3.2.显性并行指令计算(EPIC)3

1.3.3. IA-64指令集体系结构(ISA)5

1.3.4. IA-64的指令类型6

1.3.5. IA-64的指令格式6

1.3.6. IA-64体系结构的特性7

1.3.7. Itanium 1正式上市101.4.康柏决定采用IPF体系结构10二、发展现状122.1. 64位RISC微处理器的发展现状122.2. Itanium 2正式上市13

2.2.1. Itanium 2增强的体系结构14

2.2.2.指令级并行度的提高15

2.2.3.应用性能的全面提高16三、未来展望173.1. IA-64将成为主流体系结构17

3.1.1.生命力旺盛的体系结构17

3.1.2.先进的设计技术和制造工艺17

3.1.3.公平竞争的开放性平台17

3.1.4.批量生产能力18

3.1.5.与IA-32及PA-RISC的二进制兼容性18

3.1.6.强大的OEM和ISV支持以及推广实力18

3.1.7.提供新的机遇183.2. HP肩负开创IA-64计算新纪元的重任18

3.2.1.积极推行向IPF过渡的RISC处理器战略18

3.2.2.把高端系统产品全面转向IPF平台20

3.2.3.应用软件基础设施建设21

3.2.4.周全的技术支持和服务21

3.2.5.为用户原有投资提供最安全的保障213.3. Alpha的继续发展和新生21

3.3.1. Alpha 21364 (EV7)概述22

3.3.2.基于Alpha的系统是用户安全的选择23结束语24参考资料24

64位微处理器体系结构发展回顾和展望

引言

微处理器是现代计算机系统核心和引擎,它不仅提供计算机系统所需的处理能力,而且能够管理缓存、内存和互联子系统、支持整个系统实现多处理器并行计算。64位微处理器是一种用于装备高端计算机系统的芯片。这种芯片虽然产量比IA-32体系结构的X86系列为代表的32位芯片少2个数量级、价格也很昂贵(一个芯片的价格往往相当于一个高档的PC机)。但是,用它来装备的高档计算机系统的市场高达几百亿美元,再加上相关联的外设、存储系统、应用软件和服务市场,规模就更大了。64位芯片的市场竞争涉及到整个高端计算机市场、大规模信息技术应用领域的竞争。再加上企业级系统的外围服务器、客户机的选型也往往受到数据中心大型服务器的影响。因此,可以说除了目前已经作为消费品的家用PC市场外,64位芯片是整个信息技术和计算机应用市场竞争的焦点,是各大计算机厂商必争的兵家要地。

本文从回顾和分析64位微处理器历史、现状,未来发展出发,说明Intel和HP合作开发的IA-64 EPIC体系结构IPF系列的先进性和开放性以及发展潜力,它将要取代64位RISC芯片成为未来系统设计和企业应用的主流平台。本文对Alpha芯片的发展史作了回顾和评述,还分析对比各主要厂商应对这一发展潮流的64位微处理器战略和发展前景。

一、历史的回顾

二十世纪最后两个十年,人们看到RISC体系结构的兴起,并且从32位发展到64位。Alpha作为64位RISC技术的领头羊,开创了64位RISC计算的新时代。64位技术揭开了信息时代的新篇章,支持全球性Inte.net和电子商务的大型7×24网站、破译人类基因密码、数字技术的广泛应用、全球性的天气和灾害分析预报、人类对外层空间的探测都离不开各种基于64位微处理器的计算机系统。64位技术的广泛应用促使数据量爆炸性地增加,推动信息技术应用发生新革命、进入以存储为中心的新时代。

但是,RISC技术的复杂性、各厂商产品的封闭性和垄断性,又阻碍了进一步发展。人们开始意识到开放式系统的观念应该深入到处理器的层次,而不是仅仅停留在计算机和操作系统的层次上。为此,Intel和HP积极合作开发开放性的IA-64体系结构的64位微处理器产品系列(称为IPF系列)。2001年5月29日IPF系列的第一代产品Itanium正式上市。Itanium是第一个开放式的64位处理器,将会引导整个IT产业的革命,进一步深化开放式系统的发展,成为装备高端计算机系统的主流平台。

这段时间的另一件大事是康柏宣布转向IPF,与之竞争的64位RISC芯片只剩下IBM和Sun两家。正如当年RISC战胜CISC、64位取代32位一样,业内人士可以越来越清楚地看到IPF必将成为未来高端的主流平台。

1.1. RISC体系结构的发展

计算机自1946年问世以来,经历了许多重要的变革,其中最有意义的变革也许是从复杂指令集(CISC)过渡到精简指令集(RISC)体系结构。RISC体系结构和设计思想是80年代初出现的,它的基本思路是:抓住CISC指令系统指令种类太多(其中80%以上都是程序中很少使用的指令)、指令格式不规范、寻址方式太多的缺点(例如,VAX 780的指令操作类型超过1000种,而Alpha只有不到50种指令),通过减少指令种类、规范指令格式和简化寻址方式,大量利用寄存器间操作,大大简化处理器的结构、优化VLSI器件使用效率,从而大幅度地提高处理器性能、并行处理能力和性价比。到80年代后期,RISC技术已经发展成为支持高端服务器系统的主流技术,各厂商纷纷推出了32位RISC微处理器。如IBM的PowerPC和Power2,Sun的SPARC,HP的PA-RISC 7000和MIPS的R系列等。

基于32位RISC芯片的产品在取得了很大的成功,应用日益广泛、软件大量积累、在市场上也产生巨大的影响。其中,第一个影响是促使VAX走下坡路。DEC公司70年代末推出基于CISC体系结构的VAX系列和VMS操作系统,到80年代中期达到了辉煌的顶峰,成为敢于向IBM叫板的计算机业界2把手。VAX+VMS的确是非常好的计算机,但是由于DEC过分相信VAX,错过了一系列机遇包括32位RISC发展的机遇,开始走下坡路。所谓“成也VAX,败也VAX”。第二个影响是促进了利用商品化的部件来生产超级计算机。过去,超级计算机主要使用专门的向量处理机,价格非常昂贵。RISC技术使人们能够利用商品化程度很高的RISC微处理器生产出性能可以与低端向量机比美的计算机系统。这不仅促使Convex等一批以提供“买得起的巨型机”吸引客户的小巨型机公司成为昙花一现,也启示人们以更高级的RISC技术迈向超级计算的顶峰,孕育了64位RISC计算的新时代。

1.2. Alpha开创64位RISC计算新时代

计算机技术的另一重大发展是20世纪90年代实现的高端系统和应用从32位向64位过渡。这一过渡首先是从RISC微处理器开始的。最早问世的64位RISC微处理器是Alpha 21064和MIPS R4000。Alpha率先全面完成了从32位过渡到64位技术各项任务,包括64位微处理器设计和生产、从部门级、企业级到超级计算机的64位系统设计和生产、64位操作系统、中间件和应用软件的开发、64位系统集成、服务和支持,在此基础上建立了成熟的64位技术,创造了大量成功的应用实例、丰富的应用经验和应用成果,开创了64位技术应用时代。

Alpha自1992年第一代芯片问世以来,到2002年已经先后推出了三代、十多个型号的产品,2003和2004年还将推出第四代的Alpha 21364 (EV7)和EV79 (详见表1)。

表1 Alpha系列的发展历程

年份1991199519961998年中1999年2001年2003年

主要芯片EV-4EV-5EV-56EV-6EV-67EV-68EV-7/EV79

芯片名称21064211642126421364

工艺CMOS4CMOS5CMOS6CMOS6CMOS7CMOS8CMOS9

线宽0.75mm0.5mm0.35mm0.35mm0.25mm0.18mm0.125mm

主频MHz200300400-600500-600600-8001000-12001000 --1800

晶体管数1.5M9.3M9.3M15M15M15M100M

注:EV-X和EV-XX是康柏公司内部芯片名称,其中:EV是Extended VAX的缩写;X是一个数字,第一个数字(或只有一个数字)表示芯片的体系结构,第二个数字是制造工艺。如EV 67表示EV6即21264体系结构、CMOS 7制造工艺。

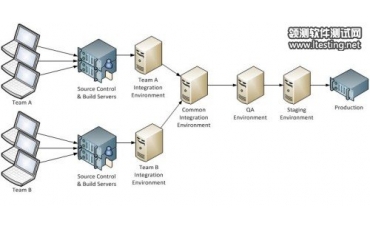

图1 2001年5月微处理器产品比较图

此后,各主要厂商也都在90年代先后推出了自己的64位RISC微处理器,包括IBM的Power和PowerPC系列、HP的PA-RISC 8000系列、Sun的UltraSPARC系列和MIPS的R10K系列等。在此期间,Alpha始终保持了性能领先的地位。图-1表示2001年5月Intel和HP合作研制的Itanium处理器问世前,各厂商微处理器产品性能的比较势态。

从左图可以看到Alpha EV67/667是当时性能最高的芯片。事实上,Alpha自问世以来几乎始终保持整数和浮点性能最高的记录,许多重要的技术突破和成功的应用实例都是在Alpha平台上实现的,如支持GB级物理内存的超大规模内存技术(VLM)、提供单一系统映象的UNIX集群、破译人类基因密码等,充分展示了64位技术的优越性和无限的潜力。到90年代末,32位芯片的“霸主”Intel也宣布与HP合作推出64位IA-64体系结构的处理器。这标志着计算机高端技术全面进入了64位的时代。今天64位计算系统已经成为高性能技术计算和电子商务应用的主流系统,推动许多新型和尖端应用飞跃发展。

1.3. Intel推出第一代IPF系列产品Itanium 1

1994年6月,Intel和HP公司签署合作协议,为服务器和工作站市场共同开发全新的64位架构。1997年11月,Intel和HP公司宣布推出基于EPIC(EPIC--Explicitly Parallel Instruction Computing;显性并行指令计算)的Itanium体系结构,并就推出产品代号为"Merced"(现名为"Itanium")的IA-64处理器系列(IPF系列)的计划。2001年5月经过7年的艰苦努力,IA-64体系结构IPF系列的第一代产品Itanium终于正式上市。

1.3.1. IA-64的基本设计思想

Inter和HP从1994年开始合作开发新型的64位芯片,它们选择了一个与大多数RISC微处理器大不相同的方向,推出了一种新的64位指令系统体系结构-IA-64。它们把这一体系结构称为EPIC(显性并行指令计算)。EPIC既不是RISC也不是CISC,它实质上是一种吸收了两者长处体系结构。IA-64的第一代芯片名为Merced,第二代芯片名为McKinley,第三代芯片名为Madison (Deerfield是它的缩小型号),目前统称为Itanium处理器系列(IPF),编号为Itanium 1,2,3。

图2 IPF产品系列发展蓝图

Itanium体系结构的设计实现基于如下的原则,使得IPF系列处理器不但能够实现持续高性能,而且具有随着技术发展进一步提高性能潜力:

●支持显性并行指令计算(EPIC);

●提供一系列有利于增强指令级并行的特性;

●把重点放在提高应用软件实际运行的性能,面向广泛范围的应用;

1.3.2.显性并行指令计算(EPIC)

众所周知,人们主要通过提高IPC(每个周期执行的指令数)和主频来提高芯片的性能。为了提高IPC,必须提高处理器指令级并行(ILP)的能力。所谓ILP是指处理器同时执行多条指令的能力,即处理器在每个时钟周期内发送和执行尽可能多条指令的能力。为此要求处理器:(1)能够找到和标识程序中可以并行执行的指令段;(2)具有充分的资源在最短时间内发送和同时执行可并行执行的指令段。这就要求处理器具有足够的智能和资源来完成这两项任务。不断探索更快速、更经济的途径完成这两项任务,推动处理器技术向前发展。

传统的RISC设计师们希望通过在芯片上增加更多的逻辑和智能(“聪明的处理器”)来提高指令并行度,同时又不必采用太高的工艺、增加太多的资源。他们把指令级并行分为静态和动态两类:静态并行在编译时由编译程序发现和处理,动态并行在运行时由处理器发现和处理。大多数现代的RISC处理器(如EV6以后的Alpha处理器)都具有这两种并行功能。例如,Alpha就设计成能够利用编译时和运行时信息。首先通过编译程序把程序改造成一个由许多可并行执行的指令段组成的记录(静态并行)。但是,许多有关程序执行过程的信息只有处理器能够在运行时了解到,例如内存访问是否命中缓存、比较指令的结果和转移指令的方向等。因此, Alpha还具有无序指令发送机制,使得处理器能够根据程序的运行实际结果、改变指令发送和执行的次序,而不会阻塞处理器的运行。这种无序执行技术的主要优点是能够在有限的工艺和资源条件下,大大提高指令并行度。最出色的例子是,Alpha EV6采用无序执行技术实现了在基于与EV56相同的0.35m工艺条件下,把性能提高了1倍以上,使芯片不仅具有高性能,而且在批量不太大的条件下具有较高的性能价格比。

虽然无序执行技术已经成为当前64位RISC芯片设计思想的主流、取得了很大的成功,但是这种技术也有其缺点,其中主要有:

(1)无序执行技术要求处理器具有较高的智能和复杂的逻辑,使得芯片的结构越来越复杂,也妨碍了主频和性能的提高;

(2)设计难度越来越大,使得许多RISC芯片的设计周期越来越长、而且经常不能按期上市,难以满足应用发展的需要;

(3)处理器在运行时没有能够充分利用编译程序所产生的许多有用的信息来提高指令并行度,也就是说传统的RISC技术没有充分发挥硬件和软件相结合的合力;

IA-64的EPIC体系结构在吸收这些教训基础上另辟蹊径,它的基本设计思想是:

(1)提供一种新的机制,利用编译程序和处理器协同能力来提高指令并行度。传统的RISC体系结构没有能够充分编译程序所产生许多有用的信息如关于程序运行线路的猜测信息,也没有充分利用现代编译程序强大的对程序执行过程的调度能力。EPIC体系结构采用创新的技术充分利用编译程序提供的信息和调度能力来提高指令并行度,同时保证在程序运行过程中发现猜测和调度有错时,处理器仍然给出正确的结果,并且尽量减少由此而带来的延迟和惩罚;

(2)在此基础上简化芯片逻辑结构,为提高主频和性能开辟道路,在工程上有一条基本原则,不是越复杂越好,而是越简捷越好,事实上,简捷的构思比复杂的构思更困难;

(3)提供大量的资源来实现EPIC,包括存储编译程序提供的信息以及提高并行计算效率所需的处理单元、缓存和其他资源。事实上,IPF系列提供远比RISC处理器丰富的资源,包括:

供指令引用的5组寄存器存储器:128个64位整数寄存器、128个82位浮点寄存器、64个1位预测寄存器、8个转移寄存器、128个专门的应用寄存器。每条指令一般引用两个输入寄存器和1个输出寄存器。

容量和性能可以随IPF系列产品升级而增加和提高的处理单元、缓存和其他资源。Itanium 1提供的此类资源已超过许多RISC处理器,Itanium 2提供的资源量又有进一步的增加;

图3 Itanium 1内部结构示意图

新出现的EPIC与传统的RISC孰优孰劣?EPIC是不是一种革命性新思想?EPIC能不能取得预期的成功?不少人还心存疑虑。对EPIC的批评和疑虑主要是:

EPIC的基本设计思想,即通过充分利用编译程序和提供必要的资源来提高性能和简化处理器逻辑,在技术上是否可行、有没有竞争力和发展前景?

EPIC使用大量芯片资源来支持并行和存储信息,必然加大芯片面积、增加芯片的成本,这在经济上是否可行、是否会使芯片价格太高而难以推广?

EPIC在注意发挥编译程序作用的同时忽视了提高处理器智能和充分利用运行时信息,使得处理器成为“迟钝的处理器”;

在处理器技术历史上,对所出现任何一种新技术的评价都离不开当时的技术发展水平和市场需求的背景、都离不开实践的检验、都不能持过于绝对化的观点:

EPIC的确需要使用大量芯片资源,这在VLSI技术发展初期的确是技术上和经济上致命的缺点,也许也是80年代Multiflow和Cydrome设计的超长指令字计算机失败的原因。即使在0.35m和0.25m线宽时代,要想象Itanium 2那样在芯片内置入2亿多个晶体管也是一个很大的负担。但是,技术的进步使得Itanium能够全面使用0.18m线宽的CMOS技术,今后还将使用0.13m和0.09m技术。在这样的技术背景下,增加芯片资源不仅在技术上可行,而且经济上负担也不大,反而能够为充分利用现代VLSI技术创造条件,使EPIC具有强大的生命力。

芯片上资源多当然有可能会增加成本。这对于批量较小的RISC处理器(例如Alpha)来说,确实较为严重。这也是Alpha的设计师们非常注意通过改进芯片逻辑设计来提高性能,十分注意避免使用过多的芯片资源的原因。但是,当前64位计算市场需求很旺、应用也已成熟,基于EPIC体系结构的IPF系列是面向广阔市场的通用和开放性产品,不但面向科学计算、而且面向企业应用,不但面向服务器、而且面向工作站。因此,IPF将主要通过批量和规模生产来降低成本,而这正是Intel的特长之一。

当然对IPF批评不是全无道理:Alpha等无序执行的RISC处理器是聪明的处理器,它的聪明之处在于能够利用动态信息来提高指令并行度。不足之处是没有保存和充分利用编译时的静态信息,不得不利用较复杂的逻辑和较高的智能来提高性能、同时能够节约芯片资源。这是处于Alpha地位的设计师们的设计思想。Itanium是一种逻辑相对简单的处理器,它的聪明之处是善于利用编译程序产生的信息和丰富的芯片资源来提高性能,不足之处是没有充分利用运行时信息,不得不使用较多的芯片资源。有时,使用动态信息效率高得多、而光使用静态信息很难解决问题,许多运算量较少、转移较多、以整数运算为主的商业应用程序就是如此。这也许就是IPF系列迄今为止,整数运算性能仍然不如浮点运算性能理想的原因。较好的方法显然是把两者结合起来,使得IPF系列吸取RISC的长处,在不过分使芯片逻辑复杂化的条件下,尽可能增加必要的智能、尽可能利用运行时信息、进而吸取Alpha等RISC处理器同时多线程(SMT)或芯片上多处理器技术。这必将进一步全面提高未来IPF系列产品的性能。

时也!势也!离开了具体的背景和立场,很难评价任何技术,批评也好、表扬也好都是相对的。但是,从技术发展的现状和未来趋势来看,EPIC将更加有利于利用VLSI技术发展的新成就如高密度CMOS技术、先进的互联和散热技术等以及大规模批量生产的市场优势。IA-64的EPIC体系结构是一种面向未来的体系结构,IPF是一个将有25年以上设计寿命的产品系列。它将随着VLSI、芯片设计、软件和系统集成技术的发展而不断发展。从实践来看,Itanium 1的上市证明了EPIC设计思想的可行性。Itanium 2的成功证明了IPF的发展潜力。IPF是Intel和HP联合开发的,再通过与康柏签订协议,获得Alpha的专利、编译程序技术、工具和技术队伍,使得IPF能够在未来充分吸取Alpha等RISC在动态并行、同时多线程、高速处理和容错性等方面的优势。人们必将越来越清楚地看到,摩尔定律的强大生命力正推动着64位微处理器的体系结构从RISC向EPIC作技术转移,EPIC是代表64位芯片发展未来的新阶段,开辟了开放性系统设计和企业应用的新时代。

1.3.3. IA-64指令集体系结构(ISA)

IA-64体系结构引入64位寻址和新的指令集,它还包含一个IA-32模式的指令集,所有IA-64处理器都能够执行IA-32程序。IA-64体系结构充分吸收了RISC体系结构的长处:只有显性装入和存储指令才能够访问内存,所有其他指令都在寄存器上操作。指令被组合在一系列3指令集束中。

图4从CISC、RISC到EPIC处理器IPC和工艺的提高

1.3.4. IA-64的指令类型

IA-64吸取RISC的经验只有很少的指令类型。表2列出IA-64的指令类型。

表2 IA-64的指令类型

类型描述执行单元类型

A整数(ALU)I-unit or M-unit

I整数(非-ALU)I-unit

M内存M-unit

F浮点数F-unit

B转移B-unit

L+X扩展I-unit

1.3.5. IA-64的指令格式

IA-64指令是很长的,每条指令41位,3条指令包装在一个集束中,每个集束用5位模版字段来描述集束的依赖性。

IA-64指令格式是为支持芯片硬件操作、实现EPIC的思想服务的:

●支持较大的寄存器存储器和丰富的寄存器间操作:IA-64的寄存器存储器拥有128项,需要7位标识符来选择寄存器。IA-64指令使用21位来标识两个输入寄存器和一个输出寄存器;

●支持EPIC风格的显性并行:IA-64每个集束中的5位模板用于描述集束内或集束间的依赖关系,允许编译程序把多个集束分在一组中,并指出所有操作是数据相关的。模板位标出一个相关操作块的结尾。这一设计允许处理器管理指令的划分,把集束联接在一起,表示一个数据相关的操作序列,还允许编译程序把任意长的可并行执行的程序段提交给硬件,从而提高处理器并行执行指令的能力;

●支持实现猜测执行、预测、高效函数调用和软件流水线等先进功能:IA-64每条指令需要一个6位的预测标识符、从一个64项的预测寄存器存储器中选择一个预测结果,支持实现猜测执行、预测、高效函数调用和软件流水线等一系列先进功能。

图5 IA-64指令集束格式和集束内指令组合

1.3.6. IA-64体系结构的特性

IA-64体系结构具有一系列特性,有利于提高处理器的持续性能,为实现IA-64利用编译程序和芯片资源提高性能并简化芯片逻辑的基本思想开辟了广阔的前景:

●大寄存器存储器:IA-64具有大寄存器存储器,128个整数寄存器和128个浮点寄存器。这一特性有两个作用:第一个作用是用以存储多次使用的数据,象RISC处理器那样大量使用寄存器间的操作,以加快数据存取的速度、避免访问内存的延迟;第二个作用是更加充分地表示程序中的并行结构。例如,为了在每个周期内发出8个操作,需要8个寄存器。如果平均地说10个周期后才读结果,则需要80个寄存器来表示并行的计算过程,允许IA-64体系结构处理器有序地(即按照指令在程序中的次序)并行地执行指令,避免象大多数RISC处理器那样,为了等待数据装入寄存器而改变指令执行次序(无序执行)、所带来的复杂性;

●编译程序与处理器的通信:Itanium体系结构提供指令模版、转移暗示和缓存暗示等机制,使编译程序能够把编译时的信息传递给处理器。此外,它允许编译出的程序使用运行时信息来管理处理器硬件,这一通信机制是最大限度地减少转移开销和缓存不命中惩罚的关键:通过允许目标程序在实际转移前把有关该转移的信息传送给硬件,能够大大减少转移的开销;在Itanium体系结构中每个内存装入和存储指令有一个2位的缓存提示字段,编译程序把对所访问的内存区域空间位置的预测信息置入其中。IPF系列的处理器可以使用这一信息来确定所访问的内存区域对应缓存区域在缓存层次结构中的位置,以提高缓存的利用效率。这一机制能够大大减少缓存不命中惩罚;

●预测机制:众所周知,在流水线机制的处理器中,转移指令开销很大。传统的体系结构中条件语句是通过转移指令来实现的。如果程序中有大量条件判断语句(如许多商业应用软件),将对处理器性能造成很大的影响。为此,IA-64引入预测机制来消除转移指令:

首先,所有IA-64指令都包含一个预测寄存器作为附加的输入,指令仅当预测正确时才被执行。因此,IA-64的指令实际上是“If(预测寄存器)指令操作”形式的,仅当指令所引用的预测寄存器为真时指令操作才被执行;

第二,为了支持预测机制,IA-64设置一条功能强大的比较指令来产生预测结果。该指令可以简化如下:pT,pF CMP(crel r2,r3)

这条比较指令使用crel给出比较规则(例如大于)比较r1和r2。比较的结果一般写入预测寄存器pT,它的相反状态写入预测寄存器pF。这给出两个预测来控制if-then-else语句的两边;

第三,IA-64的预测机制允许在编译时对程序作优化,消除转移、提高效率。例如,假定程序中原有如下的语句:if (a>b) then c=c+1 else d=d*e+f

通过编译的优化,可以消除条件语句中的转移指令,把它转化成预测执行:

pT, pF = CMP(a>b)

if (pT) C=C+1

if (pF) d=d*e+f

于是,成功地实现了通过预测机制消除了转移。此外,编译程序还可以把pT和pF后的指令调度成让处理器并行地执行它们,然后视pT和pF的状态,采用一边的结果。

●猜测机制:IA-64中有两类猜测机制:线路猜测和数据猜测。其目的都是通过提前发送操作、从关键路径中消除它的延迟,使编译程序能够提高指令级并行度、最大限度地减少内存延迟的影响。

线路猜测是指编译程序把指令移动到转移指令的前面执行。这允许提前执行程序内不命中缓存的装入指令等延迟长的操作、提高程序的执行效率。但是,当把指令移动到转移前时,可能会执行本来不应执行的指令,编译程序必须避免由此产生的副作用。为了解决这一问题,IA-64引入了两条新的指令:一条是猜测装入(sload),另一条是猜测检查(scheck)。当出现一个意外条件时,猜测装入将把检查寄存器的第65位置位,并对意外置之不理。猜测检查指令检查寄存器的第65位,如果置位,则发出意外信号。这允许把意外条件延迟到控制到达装入指令原来所在块时才加以处理,如果控制不到达该块,则永远不加以处理,从而避免执行不该执行的指令。例如,对如下的条件语句:

if (a>b) load(ld_addr1,target1)

else load(ld_addr2,target2)

由于编译时不可能知道a与b哪个大,如果提前执行两条load指令(即执行线路猜测),虽然能够得到减少延迟的好处,但也可能会产生副作用。为此,编译程序按照上述的原理,对目标作如下的调度:/* off critical path */

sload(ld_addr1,target1)

sload(ld_addr2,target2)

/* other operation including uses of target1/target2 */

if (a>b) scheck(target1,recovery_addr1)

scheck(target2,recovery_addr2)

数据猜测是指编译程序将从内存中把数据读入寄存器的指令(load指令)移动到把数据从寄存器存储到内存的指令(store指令)前面执行,从而提前从内存中读出数据、减少内存延迟的影响。例如,编译程序把下例中的load指令调度到store指令前面:

store(st_addr,data)load (ld_addr,target)

load (ld_addr,target)store(st_addr,data)

use (target)use (target)

如果在程序执行时ld_addr与st_arrd不一致,那么该程序将能够正确地享受到猜测的好处;但是,如果在执行时两个内存地址重迭,则必须采取必要的补救措施,否则就会产生错误的结果。为了防止数据猜测带来副作用,编译程序在load指令原来位置上放置一条检查指令,检查两个内存地址是否重迭。如果重迭,则转移到一段恢复程序、消除猜测所带来的副作用。于是上面的指令段变成:

/* off critical path */

aload (ld_addr, target)

/* other operations including uses of target */

store (st_addr,data)

acheck (target,recovery_addr)

use (target)

●高效的函数调用:大多数RISC处理器的函数调用需要卸出和重新装入寄存器,开销很大。IA-64增加了一个通用寄存器窗来支持高效的函数调用。这个128项的通用寄存器窗被分为一个32项的全程存储器和一个96项的堆栈存储器。IA-64允许编译程序在被调用的函数过程入口,设置一条ALLOC指令创立一个最多包含96项的新寄存器堆栈;在返回时,恢复调用程序的寄存器堆栈帧。对编译程序来说似乎有长度无限的物理寄存器堆栈,从而降低了函数调用的开支、提高了效率;如果在调用和返回时,没有足够的寄存器可供使用(堆栈溢出),那么处理器将被阻塞,等待卸出和装入寄存器,直到有足够的寄存器为止;

●软件流水线:循环步之间相互独立的循环可以象硬件流水线一样执行,即下一个循环步可以在上一个循环步结束前开始执行。这也可以称为软件流水线。传统的体系结构在同时执行多个循环步时,需要把循环拆开和软件重新命名寄存器。IA-64引入了两个新特性:旋转寄存器存储器和蕴含预测来支持软件水线。IA-64能够通过旋转寄存器机制为每个循环步提供自己的寄存器,并且不需要把循环拆开,使得软件流水线能够适用于更加广泛范围的循环,包括小的和大的循环,大大减少循环的附加开销;

IA-64的EPIC体系结构的特性有些曾经受到批评和怀疑。批评者的意见主要是:

这些特性消费的资源太多:事实上,上面的特性大多需要使用附加的芯片资源。例如,为了利用编译程序所产生的信息需要使用大量资源来存储它们,为了减少子程序调用开支需要使用寄存器堆栈,为了支持猜测需要取出if then else两边的指令等等。这种批评归根到底是在不同条件下产生不同的设计思想造成的,EPIC的设计者们有优越的条件使用最新的工艺,来缩小线宽、增加芯片资源,同时取得了简化逻辑的效果。利用资源来换取性能、简化逻辑本来就是EPIC设计思想之一。他们主要通过规模生产和扩大批量而不是通过节约资源来降低成本。RICS的设计者们(例如Alpha的设计师们)擅长于利用复杂的逻辑、在不太增加资源条件下实现高性能、保持较高的性能价格比。他们也很难通过扩大批量来降低成本。因此,他们必然对EPIC的上述特性持批评态度。究竟哪种意见对,这取决于设计者的客观条件,很难绝对地判断。但是,采用新工艺和扩大批量的发展观点来分析,EPIC的设计思想将更面向未来、有利于发挥新工艺和批量生产的潜力。

这些特性是否真正有效:Itanium 1正式上市前持这种观点的人们是比较普遍的,Itanium 2的成功使得人们逐步看清EPIC体系结构的潜力和未来发展前景。从Itanium 1到Itanium 2主频只提高了20%,而性能却提高了50%-100%。这充分说明EPIC设计思想包括上述特性,对提高指令并行度和芯片性能的有效性。

这些特性并未完全解决提高并行度的问题,有的地方还不如原来的RISC体系结构(例如充分利用运行时信息等方面):这种意见有其正确的一面。在处理器技术发展长河中,研究和发展新技术,使之提供更高并行度、适应更大规模、更复杂、更广泛应用实例,是永无穷尽的。各种技术也都有其长处和短处。因此,人们不难举出例子来说明EPIC体系结构当前的具体水平对问题规模的限制、未能解决的难点、以至不如RISC之处。EPIC技术还处于发展过程中,今后的路还很长。例如,虽然IPF系列理论上每周期可以发送6条指令,但是Itanium 1实际上平均每周期只能发送3.85条指令。Itanium 2通过改进,平均每周期已经能够发送5.7条指令(详见第二章)。正因为如此,Intel还将继续发展这一技术,推出IPF的第3代、第4代、第5代以至更后的产品。Intel还将与HP合作并且引入Alpha的技术和人员,吸收RISC技术的优点,把IPF系列推向新高峰。

1.3.7. Itanium 1正式上市

2001年5月29日Intel宣布推出IA-64体系结构IPF系列的第一代芯片Itanium 1,产生了巨大的影响:

首先,显示了IA-64的EPIC体系结构在技术上的可行性和发展潜力:EPIC与Cydrome公司(一个80年代走向失败的小巨型机公司)的VLIW (超长指令字)体系结构有一定程度的相象之处。反对者们一直期望EPIC象当年的VLIW那样走向失败,Merced一再推迟更加剧了它的困境。Itanium 1 SPECfp2000指标达到750,超过当时指标最高的EV67,SPECint2000指标达到370,超过Sun的UltraSPRAC II,最多每个周期能够执行20条指令,在高性能计算和企业应用中都表现出良好的性能。再加上IA-64在体系结构上许多优点和关键的先进特性以及Intel和HP的雄厚实力,IA-64体系结构的IPF系列产品在性能上超越RISC体系结构已经是指日可待的事情了。

第二,打破RISC的垄断,开创了开放性企业计算的新时代。众所周知,长期以来,高端计算机市场一直没有统一的标准,各厂商凭借各自专有RISC处理器芯片和专用操作系统各霸一方,形成了群雄割据的局面。这必然导致不同厂商产品之间兼容性和协同性差、系统和应用软件不一致、管理和整合的难度大、用户不得不接受各种各样的培训和认证,造成用户总拥有成本大幅度增加。Itanium 1的面市为高端计算设备市场提供第一个开放硬件平台,使得厂商和用户能够从同一开放的平台上进行系统设计划应用开发,迎来一个平等和开放的系统设计和企业计算的新时代,给整个计算机业界带来了无限的机遇和生机。

第三,实现高端硬件平台的统一、扩大批量、改善性价比。IPF系列处理器能够全面用于装备从服务器、工作站到超级计算机,面向高性能计算、Internet、电子商务和其他企业高端应用,为高端计算提供统一的平台。统一平台时代的来临,意味着生产和采购成本的大幅度降低,规模经济必然使成本与价格的大幅度下降、形成巨大的竞争优势。

虽然IA-64体系结构的IPF系列还不一定能够一统天下、真正成气候还需要假以时日,但是Itanium 1已经在微处理器发展史上揭开了新的一页,产生了巨大的影响。

1.4.康柏决定采用IPF体系结构

二十一世纪初,计算机业界另一件大事是:康柏在2001年6月宣布在Alpha EV7和EV79后,把整个高端产品系列转向IPF平台。康柏之所以采取这一重大战略行动的原因是Alpha的市场份额太小、独力难支,转向开放性的IPF平台却是大势所趋。

尽管Alpha是公认的性能最高、技术最先进的64位芯片,但它在市场上却未取得应有的成功。其原因恐怕要追溯到90年代初:1992年DEC是在错过了32位RISC的发展机遇、VAX走下坡路的形势下,推出“面向21世纪”的64位RISC处理器Alpha的。现在看来,DEC跳过32位RISC发展阶段、直接推出64位Alpha,时机选择得并不是最好,也可以说时机还没有完全成熟。就当时(90年代初)情况看,32位RISC计算机能够满足绝大多数应用需求,并且积累了大量的应用软件。真正的64位应用软件很少、Alpha的64潜力难以充分发挥。64位芯片产量小、工艺复杂、价格贵,在许多场合中反而显得大而无当、性能价格比不突出。因此,Alpha从上市的第一天开始就没有在市场上取得预期的效果。有人说是市场工作不得力,我认为主要是时机选择得不好造成的,“时也,非战之罪也”。

90年代中期后,Internet和电子商务爆炸性发展,64位需求日趋成熟、得到用户普遍认可。但是,其他厂商的64位系统产品也赶上来了。这些系统都是从原有的32位系统基础上发展起来,并且向后兼容。基于Alpha的系统成为唯一的没有相应的32位产品的64位系统。其他厂商在原有用户和32位应用基础上、从企业内部拓展市场,要比DEC挟Alpha的优势从外部进攻容易得多。所以Alpha虽然开创了64位应用的新时代,在64位市场大发展的期间,并没有占到最大的份额,在UNIX市场中大约只占5%左右份额。

康柏收购DEC时,Alpha已经失去了大部分先机:别的厂商64位RISC技术已经成长起来了、阵地也巩固了,康柏已经很难利用当时Alpha的相对优势,打入它们的阵地,只能采取面向若干重点市场的战略。其结果是:从局部看Alpha的市场份额年年扩大,从整体看收效并不明显,到2001年中,大致上占6%的市场份额。

正当康柏为了Alpha市场份额不大、却必须投入大量资金维持其技术领先地位而苦战时,情况发生了很大的变化:2001年5月,Intel的IPF第一代芯片上市了,其浮点指标超过当时最快的Alpha 21264 EV67,虽然1GHz的EV68性能指标超过第一代Itanium;但Itanium 2(Mckinley)的指标又超过EV68。面对Intel每年推出一代IPF系列新产品的迅猛发展势头,康柏应该怎么办?

摆在当时的康柏面前有两条路:第一条路是继续坚持发展Alpha,与Intel的IPF正面竞争;第二条路是及早作战略转移,过渡到IPF平台上。2001年6月康柏召开了领导层会议,专门研究对策。最后决定走第二条道路,主动进行战略转移。康柏与Intel签订了长期合作协议,把Alpha的知识产权转让给Intel、Alpha的技术队伍转移到Intel、同时把所有高端服务器AlphaServer、Himalaya和ProLiant全部转移到IPF平台上。

如果走第一条道路,即与IPF正面竞争,康柏手里还有两张牌:一张是Alpha 21364 (EV7),其性能又将超过Itanium 2,另一张是使用0.125m工艺、主频将达到1700 MHz的EV79,性能又将进一步提高。以后怎么办?继续投入巨资完成研制中的EV8以及设想中的EV9和EV10,经济上是很不合算的,也不符合时代发展潮流的。

首先,计算机应用已经进入了以解决方案和服务为中心的时代,用户关心的真正焦点是“你的计算机能够为我做什么?”“实施的速度有多快”“你能够提供何种服务和支持”。至于性能SPEC2000、TPC-C一些不大的差距,已经被放在次要地位。这种情况下,再投入巨资争性能高下,显然是很不划算的;

第二,从经济上分析,康柏每年销售10万套各种类型的基于Alpha系统(从单处理器到32个处理器),大约需要25万个芯片。康柏每年化在Alpha上研制和设计费用为2.5亿美元。换言之,每个芯片上要加上1000美元的设计费。由此可见,Alpha批量太小,争先进的负担太重了。长此以往,不仅负担不起,而且可能会造成灾难性的后果。

第三,从技术上分析,Alpha开创的许多微处理器设计技术,已经成为事实上的标准,已被业界普遍掌握和使用,竞争的重点转向制造工艺,线宽、主频、联接方式等等。这往往需要投入大量资金,康柏一家显然难以支持。Intel芯片制造年收入达到200多亿美元,盈利也数以十亿美元计,而Alpha的规模却小的多。Alpha从EV4到EV5发展速度较快,EV6开始发展速度明显放慢,EV68被推迟了1年以上,EV7推迟的时间更长。相反,Intel却能够一年推出一代IPF芯片。

康柏决定过渡到IPF是大势所趋,是明智和主动的战略转移。这一有计划的转移使得用户原来在Alpha平台上的投资得到安全的保障,Alpha的技术借IPF的发展得到新生。Alpha从EPIC最主要的竞争对手,转变为支持者,对IPF的成功发展将起极大的推动作用,一定程度上也促进了康柏与HP的合并。