嵌入式系统离线测试方法

引言

随着嵌入式系统的发展,迫切需要在嵌入式系统开发阶段对嵌入式系统进行离线测试与分析,以保证系统的软件应用程序、硬件具有兼容性、高可靠性和高可用性,迅速发现并准确定位系统中存在的问题。本文结合上海贝尔阿尔卡特股份有限公司开发的宽带交换系统,讨论离线单板硬件测试方法和系统测试方法。

离线单板硬件测试概述

在宽带交换机系统中,离线测试包括自检测试和一般的离线测试。自检测试是单板初始化完成后为了保证板子的正确运转进行的测试。它主要包括看门狗测试、快速硬件器件测试和下载通路测试。快速硬件测试完成寄存器测试和单板上单个硬件设备测试,其中又包括许多测试项。如果某一测试项测试失败,整个测试就会停止直到看门狗超时重启系统。下载测试是为了保证软件下载功能能正常工作而进行的测试。这项测试主要完成通信接口收发数据测试、中断功能测试。而一般的离线测试是在出厂检验、开发阶段中的检测和维修诊断时对上述的各测试项进行更具体的测试,以定位单板上的出错位置。

看门狗测试

在做任何一项硬件测试之前必须完成看门狗测试。这是因为一项硬件测试失败之后需要重启系统,而硬件测试的失败通常是以看门狗超时为判断条件的。这就需要看门狗在硬件测试时能正常工作。看门狗测试方法是设置并激活一个1秒的看门狗,等待1秒后系统重启。

Flash测试

在Flash中可存放程序,也可以存放数据。在烧录Flash时,可存放预先计算好的checksum值。要测试Flash时,程序重新计算checksum,然后与预先存放的值进行比较。

数据Flash的测试方法有两种。一种是非破坏性的基本测试,主要是checksum测试。另一种是破坏性的扩展测试,包括读写测试和地址/数据总线测试,具体方法与内存测试一致。基本测试可在系统自检时使用,扩展测试可在维修诊断时采用。

内存测试

内存测试可分为三类:

1. 数据总线测试: 将0001循环左移并写入内存,然后读出并比较测试。

2. 内存区测试: 对内存所有存储单元进行读写测试(读写5555H和AAAAH测试)。

3. 地址总线测试:对内存所有存储单元进行地址累加测试。从RAM的基地址起,在每一个存储单元(按照总线宽度)中写入不同的值(递增值),地址递增,直至所有的存储单元都保存不同的内容,然后读出并进行检验。

地址总线测试还可采用快速测试的方法:对0x1地址的内存单元写入地址值0x1,地址值循环左移,依次将相应的地址值写入相应的内存地址,最后检验。

在本文的系统中,自检测试时只包括内存区测试。并且,由于测试时间的限制,只是随机选择内存的一些页面进行读写测试。对于其它的内存测试方法,可以用于出厂检验、开发阶段中的检测和维修诊断。

主控芯片测试

主控芯片测试主要是对主控芯片进行定时器测试、寄存器测试、中断测试和片内RAM测试。寄存器测试是对一些特殊寄存器的功能进行测试,以验证CPU寄存器是否能正常工作。中断测试是人为产生一些硬件中断,检测主控芯片对中断的反应,是否能及时标志中断寄存器的相应标志位。片内内存测试则遵循一般内存测试规则。

PLD/FPGA简单测试

在宽带交换机系统中,较大的FPGA常实现较复杂的功能。在测试时要对相关的功能进行详细的功能测试。而对于其它简单的小型PLD/FPGA则寻求自测的方法,在PLD或FPGA的编制过程中,适当的加入一些自测手段。当主控芯片要测试它们时,设置和读取相应的PLD或FPGA的测试接口,从而获得测试结果。

PCI总线测试

PCI总线常用于连接处理器和各类外设。它提供了一个低时延路径,使处理器能够直接存取任何映射在存储器或I/O地址空间的PCI设备。它还提供一个高带宽路径,允许PCI主设备直接到主存储器存取。测试方法是先测试是否能正确读写PCI配置空间寄存器,然后测试内存映射是否可以在两端正确读写。

嵌入式系统离线测试方法

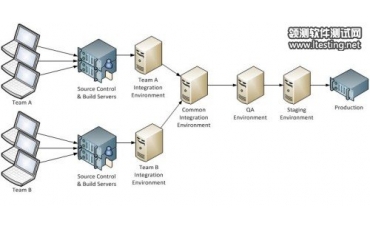

增量测试模型

在单板测试完成后,系统集成在一起之后有可能仍不能正常工作。主要原因是,模块相互调用时接口会引入许多新问题。例如,数据经过接口可能丢失;一个模块对另一模块可能造成不应有的影响;模块之间的硬件连接不正确也可能造成通信不畅;误差不断积累达到不可接受的程度等等。所以需要通过综合测试来发现各种错误。

原文转自:http://www.uml.org.cn/Test/200906047.asp