软件功能测试解决方案的评估报告

Functional testing (功能测试),也称为behavioral testing(行为测试),根据产品特征、操作描述和用户方案,测试一个产品的特性和可操作行为以确定它们满足设计需求。本地化软件的功能测试,用于验证应用程序或网站对目标用户能正确工作。使用适当的平台、浏览器和测试脚本,以保证目标用户的体验将足够好,就像应用程序是专门为该市场开发的一样。 功能测试也叫黑盒子测试或数据驱动测试,只需考虑各个功能,不需要考虑整个软件的内部结构及代码.一般从软件产品的界面、架构出发,按照需求编写出来的测试用例,输入数据在预期结果和实际结果之间进行评测,进而提出更加使产品达到用户使用的要求。 以上是属于程序软件类的测试,下面介绍应用电子技术方面的测试 印刷电路板,又称印制电路板,印刷线路板,常使用英文缩写PCB(Printed circuit board),是重要的电子部件,是电子元件的支撑体,是电子元器件线路连接的提供者。由于它是采用电子印刷技术制作的,故被称为“印刷”电路板。 在印制电路板出现之前,电子元件之间的互连都是依靠电线直接连接而组成完整的线路。现在,电路面包板只是作为有效的实验工具而存在,而印刷电路板在电子工业中已经成了占据了绝对统治的地位。 20世纪初,人们为了简化电子机器的制作,减少电子零件间的配线,降低制作成本等优点,于是开始钻研以印刷的方式取代配线的方法。三十年间,不断有工程师提出在绝缘的基板上加以金属导体作配线。而最成功的是1925年,美国的Charles Ducas 在绝缘的基板上印刷出线路图案,再以电镀的方式,成功建立导体作配线。[1] 直至1936年,奥地利人保罗·爱斯勒(Paul Eisler)在英国发表了箔膜技术[1],他在一个收音机装置内采用了印刷电路板;而在日本,宫本喜之助以喷附配线法“メタリコン法吹着配线方法(特许119384号)”成功申请专利。[2]而两者中Paul Eisler 的方法与现今的印刷电路板最为相似,这类做法称为减去法,是把不需要的金属除去;而Charles Ducas、宫本喜之助的做法是只加上所需的配线,称为加成法。虽然如此,但因为当时的电子零件发热量大,两者的基板也难以配合使用[1],以致未有正式的实用作,不过也使印刷电路技术更进一步。 1941年,美国在滑石上漆上铜膏作配线,以制作近接信管。 1943年,美国人将该技术大量使用于军用收音机内。 1947年,环氧树脂开始用作制造基板。同时NBS开始研究以印刷电路技术形成线圈、电容器、电阻器等制造技术。 1948年,美国正式认可这个发明用于商业用途。 自20世纪50年代起,发热量较低的晶体管大量取代了真空管的地位,印刷电路版技术才开始被广泛采用。而当时以蚀刻箔膜技术为主流[1]。 1950年,日本使用玻璃基板上以银漆作配线;和以酚醛树脂制的纸质酚醛基板(CCL)上以铜箔作配线。[1] 1951年,聚酰亚胺的出现,便树脂的耐热性再进一步,也制造了聚亚酰胺基板。[1] 1953年,Motorola开发出电镀贯穿孔法的双面板。这方法也应用到后期的多层电路板上。[1] 印刷电路板广泛被使用10年后的60年代,其技术也日益成熟。而自从Motorola的双面板面世,多层印刷电路板开始出现,使配线与基板面积之比更为提高。 1960年,V. Dahlgreen以印有电路的金属箔膜贴在热可塑性的塑胶中,造出软性印刷电路板。[1] 1961年,美国的Hazeltine Corporation参考了电镀贯穿孔法,制作出多层板。[1] 1967年,发表了增层法之一的“Plated-up technology”。[1][3] 1969年,FD-R以聚酰亚胺制造了软性印刷电路板。[1] 1979年,Pactel发表了增层法之一的“Pactel法”。[1] 1984年,NTT开发了薄膜回路的“Copper Polyimide法”。[1] 1988年,西门子公司开发了Microwiring Substrate的增层印刷电路板。[1] 1990年,IBM开发了“表面增层线路”(Surface Laminar Circuit,SLC)的增层印刷电路板。[1] 1995年,松下电器开发了ALIVH的增层印刷电路板。[1] 1996年,东芝开发了B2it的增层印刷电路板。[1] 就在众多的增层印刷电路板方案被提出的1990年代末期,增层印刷电路板也正式大量地被实用化,直至现在。 为大型、高密度的印刷电路板装配(PCBA, printed circuit board assembly)发展一个稳健的测试策略是重要的,以保证与设计的符合与功能。除了这些复杂装配的建立与测试之外,单单投入在电子零件中的金钱可能是很高的 - 当一个单元到最后测试时可能达到25,000美元。由于这样的高成本,查找与修理装配的问题现在比其过去甚至是更为重要的步骤。今天更复杂的装配大约18平方英寸,18层;在顶面和底面有2900多个元件;含有6000个电路节点;有超过20000个焊接点需要测试。 在朗讯加速的制造工厂(N. Andover, MA),制造和测试艺术级的PCBA和完整的传送系统。超过5000节点数的装配对我们是一个关注,因为它们已经接近我们现有的在线测试(ICT, in circuit test)设备的资源极限(图一)。我们现在制造大约800种不同的PCBA或“节点”。在这800种节点中,大约20种在5000~6000个节点范围。可是,这个数迅速增长。 新的开发项目要求更加复杂、更大的PCBA和更紧密的包装。这些要求挑战我们建造和测试这些单元的能力。更进一步,具有更小元件和更高节点数的更大电路板可能将会继续。例如,现在正在画电路板图的一个设计,有大约116000个节点、超过5100个元件和超过37800个要求测试或确认的焊接点。这个单元还有BGA在顶面与底面,BGA是紧接着的。使用传统的针床测试这个尺寸和复杂性的板,ICT一种方法是不可能的。 在制造工艺,特别是在测试中,不断增加的PCBA复杂性和密度不是一个新的问题。意识到的增加ICT测试夹具内的测试针数量不是要走的方向,我们开始观察可代替的电路确认方法。看到每百万探针不接触的数量,我们发现在5000个节点时,许多发现的错误(少于31)可能是由于探针接触问题而不是实际制造的缺陷(表一)。因此,我们着手将测试针的数量减少,而不是上升。尽管如此,我们制造工艺的品质还是评估到整个PCBA。我们决定使用传统的ICT与X射线分层法相结合是一个可行的解决方案。

Agenda 1:什么是功能测试解决方案?为什么需要功能测试解决方案?

Slide 4:功能测试的定义:

验证系统的功能性符合预定的功能说明书的测试。

Slide 5:功能测试解决方案的关键组成:

范围之内的:

范围之外的:

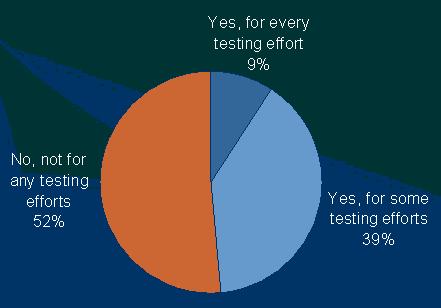

Slide 6:你的工作室有做过任何功能测试脚本的自动化吗?

通过调查北美和欧洲公司的74个决策者得出以下数据:

Slide 7:手工测试的正反面

正方:

测试用例设计的成本是最少的

- 不需要使用工具或工具专家

- 没有自动化的需要

- 不需要在测试执行之前预留提前期

可以脚本化,带探索性,或两者皆可

- 测试设计和测试执行同时进行

- 在标准的手工测试脚本设计和执行之前,之间和之后都很有用

【Kiki】需要注意一下这里所说的脚本,不是普通意思上我们说的自动化测试脚本。在美国和其他国家,他们将手工测试的测试用例用非常清晰的步骤描述,有些象我们手工测试用例中的步骤,但比那更加详细,一步一步相当清楚,不需要测试人员太多的涉及,执行下来测试人员就象一个机器人一样。

反方:

测试执行的成本很高

- 成本 = 执行时间 × 劳动率

- 执行时间很昂贵

- 当重复执行时,没有效率

脚本化的测试执行很单调

- 不需要创造力

所有的窗体都是有极高的错误倾向

- 质量取决于测试人员每时每刻的细心

- 测试结果的文档化是另一个错误的潜在来源

Slide 8:专业的工具支持可以提高脚本化手工测试的效率

工具的支持帮助手工测试人员:

Slide 9:测试自动化的正方面

正方:

- 将测试人员解放出来做更多智力型的测试(例如:探索性测试)

- 减少测试执行的时间和成本

- 允许工作室扩展测试工作的范围

反方:

- 增加了测试设计之前的投资

- 容易浪费时间在自动化“错误”的测试上 - 或用错误方法实现正确的测试

- 要求比手工测试更多的技术专家和专业工具的支持

Slide 10:一个测试自动化经济效果的简化概览

自动化一个测试脚本的成本的计算方法:

测试自动化的成本 = 工具的成本 + 脚本创建的人力成本 + 脚本维护的人力成本

何时选择自动化

自动化的成本 < 和将要执行的自动化测试的次数一样的手工执行测试的成本

例如:如果一个测试脚本在以后的两年里每星期运行一次,而且如果自动化这个测试的成本小于手工执行测试104次的成本,那么就自动化这个测试。

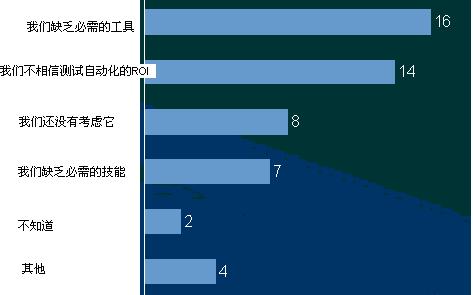

Slide 11:为什么你的公司没有执行任何的测试自动化?

通过调查38位北美和欧洲的没有执行任何测试自动化公司的决策者得出以下数据.

【Kiki】ROI:Return of Investment, 这里指的是测试自动化的投资回报。

Slide 12:由测试工作量变化产生的正确平衡

测试团队的组成

- 编程技能 vs.主题专家

- 杠杆作用每位团队成员优点的劳动力分工

- 开发团队自身测试工作量的评估

所测试应用程序的特征

- 所测试应用程序所采用的技术

- 所测试应用程序的稳定性

时间轴

- 创建自动化测试脚本的可用时间

- 应用程序的预期生命周期

Slide 13:手工和自动化测试的集成测试管理解决方案的收益

计划和监控所有测试活动的共同接口

手工和自动化测试资产的变更管理

提交来自手工测试和测试自动化工具的缺陷直接到测试管理工具里

递增的自动化测试包中的部分内容

Agenda 2:Forrester如何评估功能测试解决方案?Slide 15:我们如何决定选择哪些供应商?

参与的标准

- $10M的年税收

- 支持手工测试,测试自动化和测试管理

一些被排除的供应商

- RadView和Seapine

- 他们已经在去年的自动化工具中评估过了

- Worksoft, SDT和LogiGear

- 他们关注的是关键字驱动的测试自动化

- Agitar和Parasoft

- 关注开发人员的测试

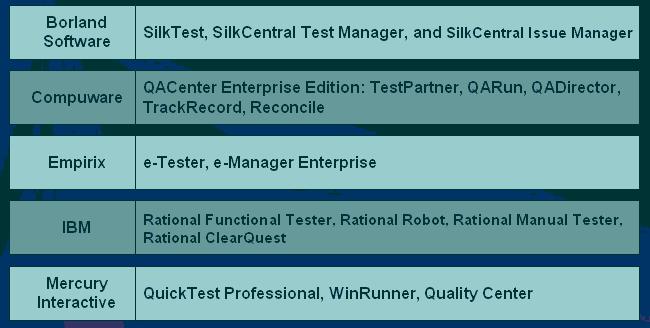

Slide 16:评估的供应商和他们相应的产品

【Kiki】补充:

Slide 17:Forrester Wave?评估的流程