SDH/SONET网络同步分层结构的时钟符合性测试

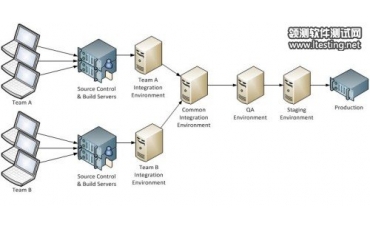

为了防止数据传输丢失,需要对一条电信网络上的所有时钟进行同步,以确保发送和接收节点以同样的速率对数据进行采样。网络同步以时钟分层结构为基础(图1),顶层时钟精度最高。

|

|

图1:SDH/SONET 网络同步分层结构。 |

分层结构中的下一层为同步供给单元(SSU)或楼宇综合定时供给(BITS)。SSU/BITS 具有保持性能,当它失去与PRC/PRS 的同步后,可以产生一个短时间内精度高于其固有自由振荡精度的时钟。SSU/BITS 通常采用由铷时钟驱动的数字锁相环(DPLL)来实现。

第三层是SDH设备时钟(SEC)或 SONET最小时钟(SMC)。SEC/SMC 也具有保持性能,但其保持和自由振荡精度性能低于对SSU/BITS的要求。SEC/SMC通常采用由恒温晶体振荡器(OCXO)或温度控制晶体振荡器 (TCXO)驱动的DPLL来实现。分层结构中的第二层及以下各层,只要其到 PRC/PRS 的路径不中断,就可以拥有与PRC/PRS相同的时钟精度。

出于可靠性原因,希望所有全球性电信网络全部同步到一个单一的PRC/PRS是不现实的。实际网络采用一种包含许多独立运行的PRC/PRS的平行时钟分布结构。每个电信提供商一般都有自己的 PRC/PRS,这意味着全球性电信网络是由一些同步孤岛通过一些准同步链路链接而成的。

PRC/PRS和SSU/BITS通常实现为只具有时钟功能(无数据传输)的独立产品,而SEC/SMC一般都作为网络产品的一部分被实现,如插分多路复用器等。

|

|

图2:MTIE 计算示例。 |

任何具有PDH或SDH/SONET接口的电信产品都必须符合相应的时钟标准。标准不是一种要克服的障碍,而是可以提高网络可靠性和不同厂商之间互操作性的一系列规范。

有两个主要标准实体,负责制定网络时钟要求。它们就是面向北美地区的Telcordia和面向世界其他地区的ITU。Telcordia 要求通过GR-XXX-CORE 规范来规定,而ITU则通过ITU-T G.XXX 系列文档覆盖网络时钟部分。图1说明了与时钟分层结构的不同层次相应的ITU和 Telcordia标准。

通信系统中的损伤

抖动和漂移被定义为数字信号在时间上偏离其理想位置的短期变动和长期变动。

本质上,抖动和漂移是通常用来描述数字信号相位噪声的术语。完全定义相位噪声的两个参数是幅度和频率。频率低于10Hz的相位噪声称为漂移,而频率等于或高于10Hz的相位噪声称为抖动。

如果对于一个具有相位噪声的时钟,使用以相同频率但没有相位噪声的时钟触发的示波器来对其进行观察,我们将会看到,时钟的上升沿和下降沿模糊不清(时间上定义不清晰)。如果时钟具有低频相位噪声(漂移),我们会看到上升沿和下降沿实际上正在以等于漂移频率的速率前后移动。这种移动的范围定义为抖动/漂移的幅度。网络通信中的抖动幅度以单位时间间隔(UI)来表示,其中UI等于时钟周期。电信网络中的相位噪声图在时域中通常表现为任意形状。因此,其频谱不是离散的,尽管它可能会含有一些离散分量。

|

|

图3:典型电信系统中的时钟。 |

* SDH/SONET 网络中的指针调整,它允许虚容器 (VC)/虚支路(VT)在一个 STM-N/OC-N 帧之内前后移动。指针调整用于补偿 VC/VT和STM-N/OC-N 的时钟之间的相位变化。指针调整按一个字节的步幅进行,因而会产生较大幅度的相位噪声。

* 位调整(Bit justification),用于当 PDH 信号映射到 VC/VT 时对PDH和STM-N/OC-N信号之间的分数频率差异进行补偿。因位调整引起的相位噪声的频率与PDH和STM-N/OC-N信号之间的分数频率差异成正比。

* PDH网络中的位填充(Bit stuffing),用于对低层信号进行异步多路复接,形成一路高层 PDH 信号。例如,位填充被用于将四路异步E1信号复接成一路E2信号。

* 传输介质(光纤、铜)传播延迟变化,由温度变化引起,也称为日漂移(diurnal wander)。由于环境温度变化很慢,这种类型的漂移一般频率很低。

* 同步元件(DPLL)中的固有漂移。网络通信中使用的 DPLL 通常具有很窄的环路带宽,以便更有效地从输入参考信号中滤除抖动和漂移。虽然窄环带宽对于从参考信号中滤除相位噪声十分有效,但它无法滤除用作 DPLL 主时钟的晶体振荡器产生的本地相位噪声。DPLL

|

|

图4:时钟品质鉴定测试装置。 |

时钟标准以滤波后抖动的最大幅度(以UI为单位的峰-峰值)来规定抖动要求,而漂移则是以最大时间间隔误差(MTIE)和时间偏差(TDEV)来规定的。

时间间隔误差(TIE)显示了被测时钟的边沿相对于理想时钟的边沿在时间上偏离的程度。并不是对时钟的每个连续边沿都进行测量,而是通常间隔 30 ms,以降低采集的数据量(一般需持续 27 小时),同时高速变化(抖动)也不是此处所考虑的。TIE 通常以[ns]表示,但也可以使用[us]和UI为单位来表示。

MTIE是通过对TIE数据进行计算,寻找一个滑动窗口内TIE的最大(峰-峰)变化而得到的,如图2所示。

首先,我们从宽度等于两个TIE样本间时间(?0) 的最小窗口开始,使其滑过TIE测量期间并找到 MTIE(?0)。接着,增大滑动窗口的尺寸并找到新窗口的 MTIE(2*?0)。重复这一过程,直到滑动窗口的尺寸等于测量期间 (N*?0)。此过程可使用以下公式来表示。

|

|

|

n = 1, 2, ..., N

MTIE特别适合用于估计帧调节器中使用的环形缓冲区的最小尺寸,用于补偿将数据写入环形缓冲区的线路时钟(提取时钟)与由时钟卡 DPLL 和线路卡 DPLL/APLL 产生的、用于从缓冲区中读取数据的本地时钟之间的相位误差。

尽管 MTIE 对于表征最大相位误差非常有用,但它不含关于漂移频谱的任何信息。漂移的频谱,连同造成漂移的噪声过程类型一起,可通过TDEV获得。可通过TDEV检测和量化的噪声有:白相位噪声、闪烁相位噪声、白频率噪声、闪烁频率噪声以及随机漫步频率噪声。

TDEV以统计的方式通过积分时间展示了时钟相位偏离理想时钟的程度。由于频率是时间的倒数,因此较小的积分时间表示存在较高的漂移频率分量,而较大的积分时间则表示存在较低的频率分量。可以看到,TDEV 等效于通过一个中心频率为 0.42/?的带通滤波器测得的均方根相位噪声功率,其中?为 TDEV积分时间。

TDEV是通过从 TIE 样本取得二阶差分而计算得到的,其计算如下:

|

|

|

其中n = 1, 2,..., 积分元件 (N/3)

TDEV对系统性误差不敏感,如被测时钟与测试仪使用的“理想”时钟之间的固定频率偏移等。

相位瞬态

出于冗余的目的,任何网络节点都必须接收至少两个同步参考时钟。相位瞬态是指相位相对于其理想位置的突然移动:当网络节点的同步参考时钟突然中断时,就会发生这种情况。

|

|

图5:典型漂移产生 MTIE 和 TDEV 测试结果。 |

长期相位瞬态发生在没有冗余同步参考时钟可用的时候。在这种情况下,网络节点时钟将转入保持模式,相位误差以正比于保持精度的速率继续增大。保持模式将在“时钟卡”部分进行说明。最大允许相位瞬态采用 MTIE 和最大相位斜率来规定。

典型电信系统

电信系统必须在所有网络条件下提供高度可靠的操作。为此,应对系统内最关键的组件进行冗余备份,包括时钟。

典型系统的时钟包含两个时钟卡,它们通过一个公共后接线板向多个线路卡馈送时钟,如图 3 所示。所有线路卡均同步于来自活动时钟卡的时钟。如果活动时钟卡时钟失败(例如,卡未插入),线路卡将同步到来自冗余时钟卡的时钟。从一个时钟卡切换到另一个时钟卡不得在系统中引起任何中断或失败。时钟卡冗余的实现细节请参阅参考文献 [1]。

时钟卡

使用两个时钟卡可以防止一个卡失败时造成内部故障。正如图 3 所示,为了防止外部时钟参考失败,时钟卡设计成能够同步到多个参考时钟。

一个时钟卡从多个源接收参考时钟,选择一个,使用一个DPLL对其进行相位噪声滤波,然后通过后接线板将其分配到线路卡上。DPLL是时钟卡中最重要的元件。时钟卡 DPLL参考时钟可来自外部的一个 SSU/BITS,来自内部的线路卡或系统中的其他时钟卡。根据产品的目标应用和部署区域,DPLL需要符合相应的时钟规范,如 Telcordia GR-1244 CORE、Telcordia GR-253-CORE 或 ITU G.813。DPLL 需能够提供一组重要特性,包括:

* 无中断参考时钟切换:如果 DPLL 锁定的参考时钟失败,DPLL 将锁定到另一个可用的参考时钟上,且不会在其输出上出现相位扰动。

* 保持模式:DPLL 连续计算锁定参考时钟的平均频率。如果参考时钟失败,且没有其他参考时钟可用,DPLL 将转入保持模式,并根据计算的平均值产生一个输出时钟。保持稳定性取决于 DPLL 平均算法的分辨率和用作该 DPLL 主时钟的振荡器的频率稳定度。

* 参考时钟监测:DPLL 需要连续监测其输入参考时钟的质量。如果 DPLL锁定的参考时钟恶化(消失或频率漂移),DPLL将发出报警(中断)并切换到另一个有效参考时钟。

* 窄环带宽:DPLL 可被视为一个相位噪声滤波器。环路带宽越窄,相位噪声衰减越好。一些规范,如 G.813,明确规定了环路带宽。其他标准,包括

|

|

图6:典型相位噪声转移测试结果。 |

* 高抖动和漂移容差:DPLL 应能够容许其输入上有较大相位噪声而仍能保持同步。

成本最低且最简单的时钟卡设计方法是使用一个能够保证时钟性能需求的、现成的单片 DPLL。另外一种选择是使用有些晶体振荡器厂商提供的一种混合模块 DPLL。但是,模块方法一般要比单片 DPLL方法贵很多,并且要求更大的电路板面积,功率也更大。第三种选择是开发一种自行研发的 DPLL。这种策略风险很大,因为即使拥有自主研发时钟专家,要开发一种符合时钟规范的 DPLL仍需要一个很长的开发周期,其中包括很多反复。表1对这三种方法进行了比较。

线路卡

如图 3 所示,每个线路卡具有一个 DPLL,后跟一个模拟 PLL(APLL)。DPLL用于实现活动时钟和冗余时钟之间的无中断切换,提供短时间内时钟的持续,例如当活动时钟意外消失,而系统未检测到活动参考时钟失败,并切换,锁定于提供冗余参考时钟的线路卡 DPLL 之前。一个线路卡 DPLL需要有一个晶体振荡器(同任何 DPLL一样)。但是,这种振荡器可以是低成本振荡器,因为线路卡 DPLL不需要转入保持模式(除了在活动和冗余时钟之间切换时的短暂时间)。对于长期保持,系统将依赖于时钟卡 DPLL。因此,时钟卡 DPLL 要求使用质量较高的晶体振荡器 (TCXO, OCXO)。

APLL 只用于抖动减小和倍频。使用 APLL可以实现无中断参考时钟切换。但是,很难获得良好的时钟持续性,因为相对于使用晶体振荡器的 DPLL 而言,APLL中通常使用的基于 LC 的振荡器具有很低的保持稳定性。典型地,一个 DPLL的短期保持精度为 0.01ppm(百万分之一)或更优,而一个 APLL的保持精度却在 100ppm以上。

时钟符合性测试

虽然 PLL对于时钟符合性来说是最重要的装置,但所有时钟规范要求却都没有对其性能做出特别的规定。时钟规范是为网络产品(插分多路复用器、路由器等)而不是仅仅针对 PLL制定的。符合性是在网络产品数据接口(E1/T1、STM-1/OC3 等)而非时钟层次(PLL 输出)上进行测试的。

市场上有可以进行完整的标准符合性测试的设备。最常用的有安科特纳(Acterna)公司的 ANT-20和安捷伦公司的OmniBER。图4显示了一种典型的测试装置。

虽然时钟规范要求是在网络接口上测试的,但出于调试的目的,同时也在时钟层次上进行测试将会非常有用。例如,如果我们在网络接口上进行的抖动产生测试中失败,我们无法确定失败是否是由线路卡 PLL、扇出缓冲器、或是帧调节器/LIU 造成的,除非我们在时钟层次上进行抖动产生测试。

|

|

图7:典型相位噪声容限测试结果。 |

对于较高级别的Sonet/SDH,其最大允许抖动为皮秒范围,这时相位噪声分析仪将是必不可少的。这是因为它们可以测量亚皮秒抖动,并可提供对相位噪声频率分布的观察,可方便地对相位噪声进行滤波和积分。

抖动产生

抖动产生要求规定了当提供干净(无抖动)输入参考时钟时,被测设备(EUT)产生的最大固有抖动量。最大固有抖动是以通过一个一阶带通滤波器测量时得到的以 UI为单位的峰-峰值来规定的。最关键的抖动产生元件是线路卡 DPLL 和 APLL、LIU(SerDes)和光学模块。确保设计可靠性,因为 LIU和光学模块一般总会增加抖动,设计DPLL+APLL的预计抖动产生应至少比规范要求低 50%。抖动产生可使用图 4 中所示的测试装置进行测量。因为抖动产生是在使用一个干净输入参考时钟的情况下进行测量的,因此应禁用测试仪内部的抖动/漂移产生模块。

漂移产生

漂移产生要求规定了当提供极为稳定的无漂移输入参考时钟时,被测设备(EUT)产生的最大固有漂移量。漂移产生要求采用 MTIE和TDEV模板(mask)来定义。图5显示了典型的漂移产生 MTIE和TDEV测试结果。

固有漂移主要依赖于时钟卡DPLL的带宽和用作时钟卡 DPLL主时钟的晶体振荡器的短期频率波动。当提供干净输入参考时钟时,DPLL可以对那些短期频率波动进行补偿并在其输出上提供干净时钟。DPLL的此项能力依赖于其带宽--带宽越宽,补偿越好。由于规范对 DPLL的带宽做出了规定,因此唯一的变量就是晶体振荡器。因为线路卡 DPLL一般都具有较宽的带宽,因此其晶体振荡器不必很稳定。

进行漂移相关的测试时,总是需要使用一个具有高精度和稳定性的外部时钟。典型的情况是,测试仪被提供一个源于 PRC/PRS 的时钟,如 GPS或提供一个如图4所示的铷时钟源。

相位噪声(抖动和漂移)转移

相位噪声转移表示了输出和输入相位噪声之间的比率与相位噪声频率的关系。其定义为:

|

|

|

实质上,它表示了 EUT 将从哪个频率开始衰减相位噪声。它还显示了 EUT在通带区域内是否存在任何相位噪声峰化(增益)。图6显示了一种典型的 EUT 相位噪声转移曲线。

相位噪声转移主要受时钟卡 DPLL影响,因为 PLL 可以被看作是相位噪声的低通滤波器。EUT 时钟链中的其他 PLL(时钟卡 DPLL和 APLL)的影响不是很重要,因为它们的环路带宽比时钟卡 DPLL 的环路带宽要宽得多。

相位噪声转移和抖动产生的测试装置是相同的(图 4)。伪随机数据被调制以正弦相位噪声,然后馈送至 EUT。EUT的输出反馈到测试仪,在这里,时钟被从数据中提取并馈送到一个抖动/漂移测量计。对不同的相位噪声频率重复进行上述测量。测试仪产生的相位噪声的幅度应当对所有测量恒定不变,其选择应小于 EUT 在最高相位噪声频率时的相位噪声容差。

|

|

表1:时钟卡实现方法比较。 |

相位噪声(抖动和漂移)容限

相位噪声容限规定了 EUT仍能保持同步而不产生任何数据丢失或报警时所能容许的最小相位噪声量。用于相位噪声容差测量的测试装置如图 4 所示。伪随机数据被调制以正弦相位噪声,然后馈送至 EUT。EUT 的输出反馈到测试仪,在那里对位差错和报警进行检查。相位噪声幅度缓慢增大,直到测试仪检测到位差错或报警。对不同的相位噪声频率重复进行上述测量。如图 7 所示,测得的相位噪声容限值与来自目标时钟规范的相位噪声容限模板进行比较。

与漂移转移类似,Telcordia 规范(GR-1244-CORE 和 GR-253-CORE)以及针对1.544 Mbps 层次的 ITU 规范(G.813 中第 2 项)不使用正弦漂移进行漂移容限测试。两种规范均建议使用与对 TDEV 所定义的频谱一样宽的频谱的漂移。

短期相位瞬态

短期相位瞬态规定了 EUT在两个同步参考时钟之间切换时其输出上的最大相位误差和最大相位斜率。测试装置与图 3 中的装置类似,不同之处在于,需要使用一个额外的测试仪产生一个第二参考时钟。测试是通过断开活动参考时钟,从而引起 EUT 时钟(时钟卡 DPLL)切换到辅助时钟源而进行的。短期相位瞬态采用 MTIE 模板(mask)规定。

短期相位瞬态主要依赖于时钟卡 DPLL 参考时钟切换机制。

长期相位瞬态(保持)

长期相位瞬态规定了当 EUT 处于保持模式时相位的最大偏移。它采用测量时钟和“理想”时钟之间的分数频率偏移和频率漂移进行量化表示。G.813 第 1 项中的最大相位误差定义如下:

|

|

|

其中:

(方程5)对应于初始频率偏移,定义为 50 ns/s

(方程6)是因温度变化引起的频率偏移,等于 2000 ns/s。如果没有温度变化,则其等于零。

(方程7)是由老化引起的频率漂移。规定为

|

|

|

保持完全依赖于时钟卡 DPLL及其主时钟晶体振荡器的稳定性。特别地,初始保持精度(方程5)依赖于 DPLL平均算法的分辨率,而其他参数则依赖于晶体振荡器的稳定性。

参考文献

[1] Slobodan Milijevic, Adding Timing Redundancy to Comm Equipement Designs, Communications System Design Magazine, Dec. 2004

[2] Definitions and terminology for synchronization networks ITU-T Recommendation G.810, 1996

[3] Timing characteristics of SDH equipment slave clocks (SEC) ITU-T Recommendation G.813, 1998

[4] Synchronous Optical Network (SONET) Transport Systems: Common Generic Criteria GR-253-CORE, Issue 3, 2000

[5] Clocks for the Synchronized Network: Common Generic Criteria GR-1244-CORE, Issue 2, 2000

作者:Slobodan Milijevic

Email: slobodan.milijevic@zarlink.com

卓联半导体公司